E210 Engineering Cyber-Physical Systems (Spring 2021)

## Serial Peripheral Interface (SPI)

**Bryce Himebaugh**

| Weekly Focus          | Reading           | Monday                   | Wed                    | Lab                           |

|-----------------------|-------------------|--------------------------|------------------------|-------------------------------|

| Exam/CPS Introduction | Ref 1 Chapter 1   | 3/8: Exam 1              | 3/10: CPS Introduction | Project 5 Raspberry PI Setup  |

| Raspberry Pi          | Ref 2 Chapter 1-3 | 3/15: Pi Intro/UART Bus  | 3/17: Git/Github       |                               |

| I2C Bus               | Ref 3             | 3/22: I2C Bus            | 3/24: Wellness Day     | Project 6 I2C Pressure Sensor |

| Python/Sensor         | Ref 4, Ref 5      | 3/29: Classes/Modules    | 3/31: Pressure Sensor  |                               |

| SPI                   | Ref 6             | 4/5: SPI Bus Overview    | 4/7: SPI HDL Design    | Project 7 SPI Connected I/O   |

| SPI                   | Ref 7 Chapter 1   | 4/12: SPI HDL Design     | 4/14: Sensor Memory    |                               |

| Network Interface     | Ref 7 Chapter 2   | 4/19: Ethernet Interface | 4/21: MQTT             | Project 8 Network Interface   |

| MQTT/Flask            | Ref 7 Chapter 14  | 4/26: Flask              | 4/29: Open Topic       |                               |

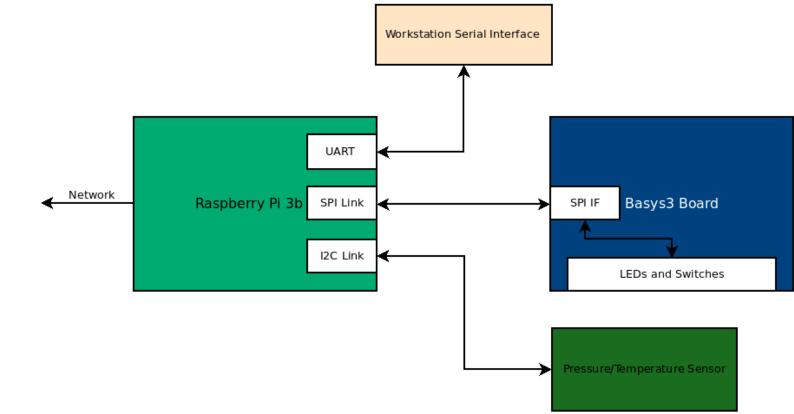

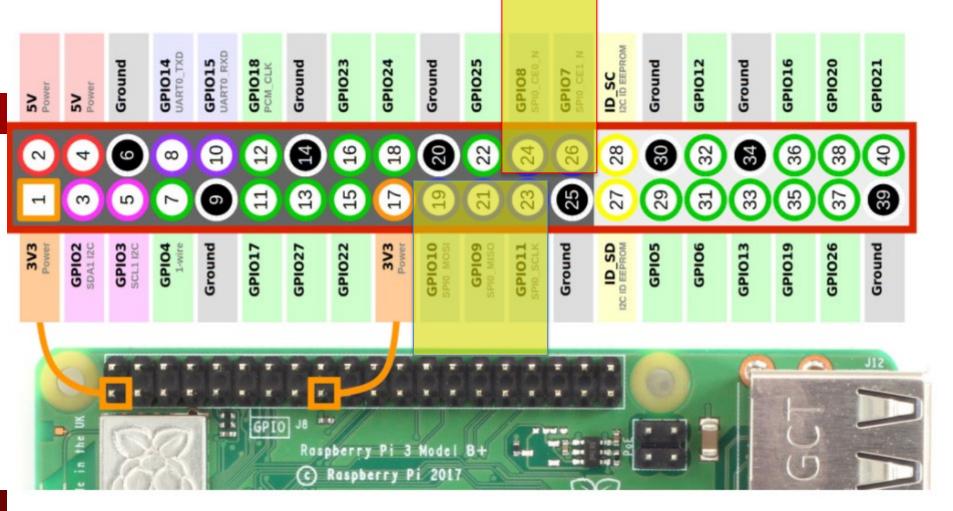

#### Raspberry SPI Link

U INDIANA UNIVERSITY BLOOMINGTON

# **SPI Overview**

#### What is I2C?

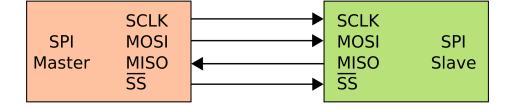

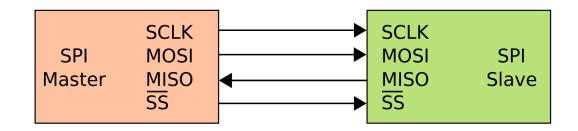

- 1. Synchronous Serial Link

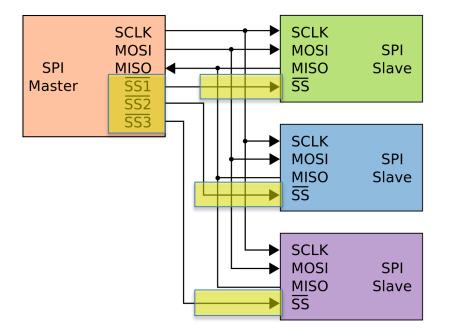

- 2. 4 Wire Bus

- 3. Devices Selected with Chip Select Pin

- 4. Full Duplex

- 5. Only One Bus Controller

## History of I2C

- Developed by Motorola in mid-80s

- Short distance communication for embedded systems

- De facto standard

- Significantly faster than I2C or UART communication

- Max Speeds Typically 20Mbps+ (no minimum speed)

- Used in SD Cards and Embedded LCD displays

| Category                          | SPI                        | I2C                        | UART                               |

|-----------------------------------|----------------------------|----------------------------|------------------------------------|

| Clock                             | Synchronous                | Synchronous                | Asynchronous                       |

| Speed                             | 20 Mbps +                  | 400K Baud (5M Baud<br>Max) | 115K Baud                          |

| Transmission Mode                 | Full Duplex                | Half Duplex                | Full Duplex                        |

| Number of Devices                 | Only Limited by CS<br>Pins | 112 (1024 possible)        | 2                                  |

| Number of Pins                    | 3 + CS                     | 2 (Data, Clock)            | 2* (Rx, Tx), Optional<br>(CTS,RTS) |

| Baud Rate Accuracy<br>Requirement | N/A                        | N/A                        | ~3% Baud Rate<br>Accuracy          |

| Development Complexity            | Low                        | Med                        | Low                                |

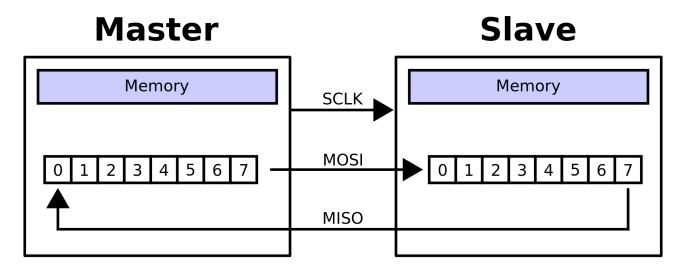

# **Device Naming Conventions**

### **Open Source Hardware Association**

| New Name              | Old Name                   |

|-----------------------|----------------------------|

| SDO – Serial Data Out | MOSI – Master Out Slave In |

| SDI – Serial Data In  | MISO – Master In Slave Out |

| CS – Chip Select      | SS – Slave Select          |

| SCLK - Clock          | SCLK-Clock                 |

https://www.oshwa.org/a-resolution-to-redefine-spi-signal-names

٦ſ

# **Bus Connections**

### **Single Peripheral**

#### **Multiple Independent Peripherals**

# **Bus Protocol**

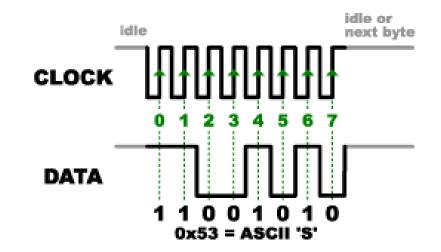

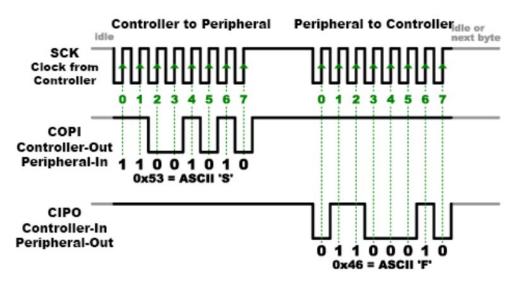

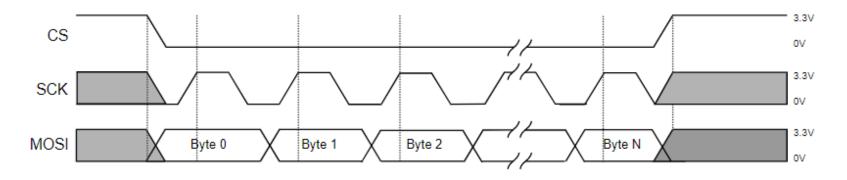

### **Sending Data**

https://learn.sparkfun.com/tutorials/serial-peripheral-interface-spi/all

### **Receiving Data**

https://learn.sparkfun.com/tutorials/serial-peripheral-interface-spi/all

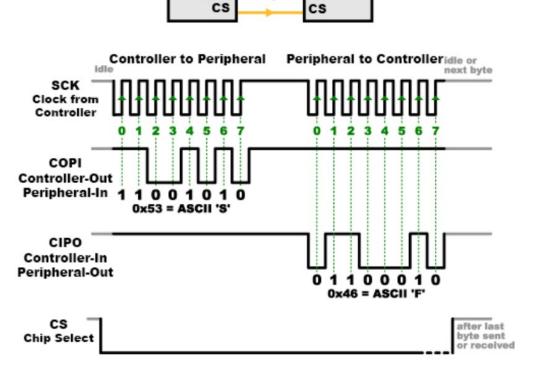

#### **Chip Select**

SCK

COPI

CIPO

SCK

COPI

CIPO

#### 16-bit Shift Register (split between two chips)

Swaps Registers

BL

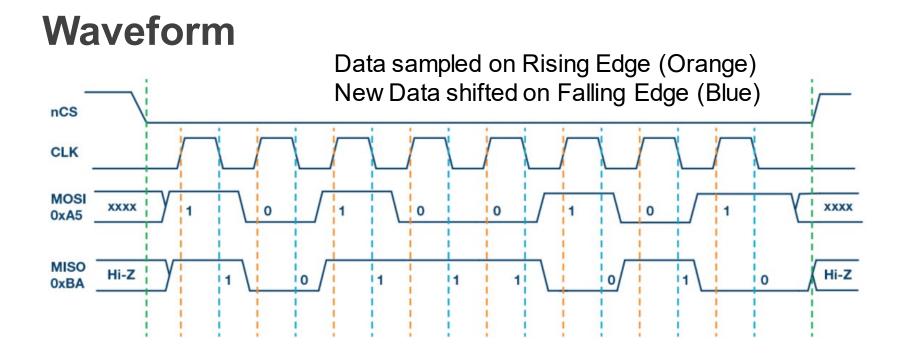

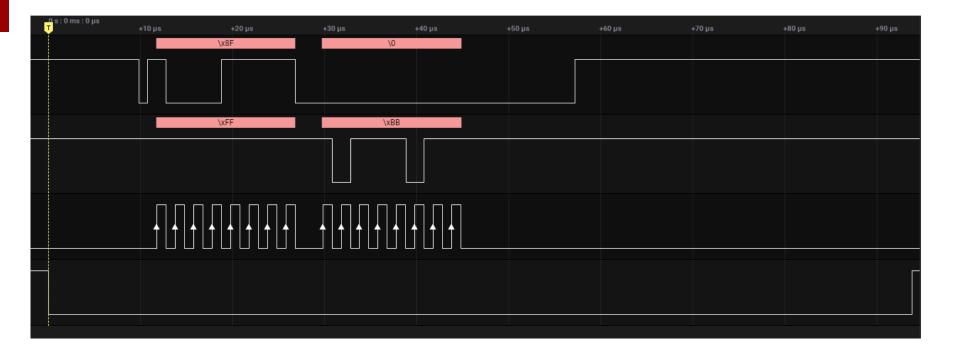

#### Waveform

Figure + Frample of a SPI transmission

```

* Simultaneously transmit and receive a byte on the SPI.

* Polarity and phase are assumed to be both 0, i.e.:

- input data is captured on rising edge of SCLK.

- output data is propagated on falling edge of SCLK.

* Returns the received byte.

*/

uint8 t SPI transfer byte(uint8 t byte out)

uint8 t byte in = 0;

uint8 t bit;

for (bit = 0x80; bit; bit >>= 1) {

/* Shift-out a bit to the MOSI line */

write MOSI((byte out & bit) ? HIGH : LOW);

/* Delay for at least the peer's setup time */

delay(SPI_SCLK_LOW_TIME);

/* Pull the clock line high */

write SCLK(HIGH);

/* Shift-in a bit from the MISO line */

if (read MISO() == HIGH)

byte in |= bit;

/* Delay for at least the peer's hold time */

delay(SPI SCLK HIGH TIME);

/* Pull the clock line low */

write SCLK(LOW);

return byte in;

```

```

* Simultaneously transmit and receive a byte on the SPI.

* Polarity and phase are assumed to be both 0, i.e.:

- input data is captured on rising edge of SCLK.

- output data is propagated on falling edge of SCLK.

* Returns the received byte.

*/

uint8 t SPI transfer byte(uint8 t byte out)

uint8 t byte in = 0;

uint8 t bit;

for (bit = 0x80; bit; bit >>= 1) {

/* Shift-out a bit to the MOSI line */

write_MOSI((byte_out & bit) ? HIGH : LOW);

/* Delay for at least the peer's setup time */

delay(SPI_SCLK_LOW_TIME);

/* Pull the clock line high */

write SCLK(HIGH);

/* Shift-in a bit from the MISO line */

if (read MISO() == HIGH)

byte in |= bit;

/* Delay for at least the peer's hold time */

delay(SPI SCLK HIGH TIME);

/* Pull the clock line low */

write SCLK(LOW);

return byte in;

```

```

* Simultaneously transmit and receive a byte on the SPI.

* Polarity and phase are assumed to be both 0, i.e.:

- input data is captured on rising edge of SCLK.

- output data is propagated on falling edge of SCLK.

* Returns the received byte.

*/

uint8 t SPI transfer byte(uint8 t byte out)

uint8 t byte in = 0;

uint8 t bit;

for (bit = 0x80; bit; bit >>= 1) {

/* shift-out a bit to the MOST line */

write MOSI((byte out & bit) ? HIGH : LOW);

/* Delay for at least the peer's setup time */

delay(SPI_SCLK_LOW_TIME);

/* Pull the clock line high */

write SCLK(HIGH);

/* Shift-in a bit from the MISO line */

if (read MISO() == HIGH)

byte in |= bit;

/* Delay for at least the peer's hold time */

delay(SPI SCLK HIGH TIME);

/* Pull the clock line low */

write SCLK(LOW);

return byte in;

```

INDIANA UNIVERSITY BLOOMINGTON

```

* Simultaneously transmit and receive a byte on the SPI.

* Polarity and phase are assumed to be both 0, i.e.:

- input data is captured on rising edge of SCLK.

- output data is propagated on falling edge of SCLK.

* Returns the received byte.

*/

uint8 t SPI transfer byte(uint8 t byte out)

uint8 t byte in = 0;

uint8 t bit;

for (bit = 0x80; bit; bit >>= 1) {

/* Shift-out a bit to the MOSI line */

write MOSI((byte out & bit) ? HIGH : LOW);

/* Delay for at least the peer's setup time */

delay(SPI SCLK LOW TIME);

/* Pull the clock line high */

write SCLK(HIGH);

/* Shift-in a bit from the MISO line */

if (read MISO() == HIGH)

byte in |= bit;

/* Delay for at least the peer's hold time */

delay(SPI SCLK HIGH TIME);

/* Pull the clock line low */

write SCLK(LOW);

return byte in;

```

```

* Simultaneously transmit and receive a byte on the SPI.

* Polarity and phase are assumed to be both 0, i.e.:

- input data is captured on rising edge of SCLK.

- output data is propagated on falling edge of SCLK.

* Returns the received byte.

*/

uint8 t SPI transfer byte(uint8 t byte out)

uint8 t byte in = 0;

uint8 t bit;

for (bit = 0x80; bit; bit >>= 1) {

/* Shift-out a bit to the MOSI line */

write MOSI((byte out & bit) ? HIGH : LOW);

/* Delay for at least the peer's setup time */

delay(SPI_SCLK_LOW_TIME);

/* Pull the clock line high */

write SCLK(HIGH);

/* Shift-in a bit from the MISO line */

if (read MISO() == HIGH)

byte in |= bit;

/* Delay for at least the peer's hold time */

delay(SPI SCLK HIGH TIME);

/* Pull the clock line low */

write SCLK(LOW);

return byte in;

```

```

* Simultaneously transmit and receive a byte on the SPI.

* Polarity and phase are assumed to be both 0, i.e.:

- input data is captured on rising edge of SCLK.

- output data is propagated on falling edge of SCLK.

* Returns the received byte.

*/

uint8 t SPI transfer byte(uint8 t byte out)

uint8 t byte in = 0;

uint8 t bit;

for (bit = 0x80; bit; bit >>= 1) {

/* Shift-out a bit to the MOSI line */

write MOSI((byte out & bit) ? HIGH : LOW);

/* Delay for at least the peer's setup time */

delay(SPI_SCLK_LOW_TIME);

/* Pull the clock line high */

write SCLK(HIGH);

/* Shift-in a bit from the MISO line */

if (read MISO() == HIGH)

byte in |= bit;

/* Delay for at least the peer's hold time */

delay(SPI SCLK HIGH TIME);

/* Pull the clock line low */

write SCLK(LOW);

return byte in;

```

```

INDIANA UNIVERSITY BLOOMINGTON

```

```

* Simultaneously transmit and receive a byte on the SPI.

* Polarity and phase are assumed to be both 0, i.e.:

- input data is captured on rising edge of SCLK.

- output data is propagated on falling edge of SCLK.

* Returns the received byte.

*/

uint8 t SPI transfer byte(uint8 t byte out)

uint8 t byte in = 0;

uint8 t bit;

for (bit = 0x80; bit; bit >>= 1) {

/* Shift-out a bit to the MOSI line */

write MOSI((byte out & bit) ? HIGH : LOW);

/* Delay for at least the peer's setup time */

delay(SPI_SCLK_LOW_TIME);

/* Pull the clock line high */

write SCLK(HIGH);

/* Shift-in a bit from the MISO line */

if (read MISO() == HIGH)

byte in |= bit;

/* Delay for at least the peer's hold time */

delay(SPI SCLK HIGH TIME);

/* Pull the clock line low */

write SCLK(LOW);

return byte in;

```

```

* Simultaneously transmit and receive a byte on the SPI.

* Polarity and phase are assumed to be both 0, i.e.:

- input data is captured on rising edge of SCLK.

- output data is propagated on falling edge of SCLK.

* Returns the received byte.

*/

uint8 t SPI transfer byte(uint8 t byte out)

uint8 t byte in = 0;

uint8 t bit;

for (bit = 0x80; bit; bit >>= 1) {

/* Shift-out a bit to the MOSI line */

write MOSI((byte out & bit) ? HIGH : LOW);

/* Delay for at least the peer's setup time */

delay(SPI_SCLK_LOW_TIME);

/* Pull the clock line high */

write SCLK(HIGH);

/* Shift-in a bit from the MISO line */

if (read MISO() == HIGH)

byte in |= bit;

/* Delay for at least the peer's hold time */

delay(SPI SCLK HIGH TIME);

/* Pull the clock line low */

write SCLK(LOW);

return byte in;

```

# **Register Addressing**

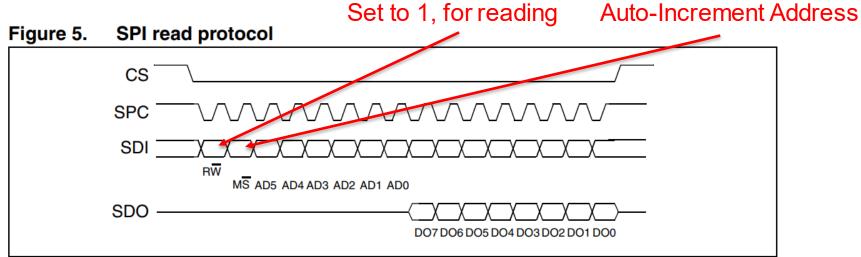

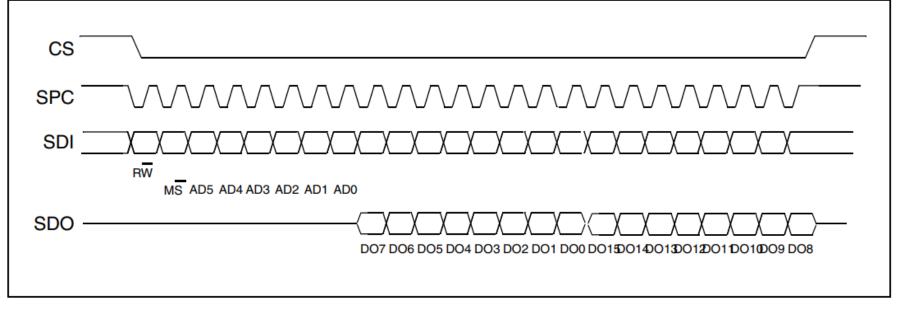

### Reading

The SPI Read command is performed with 16 clock pulses. The multiple byte read command is performed adding blocks of 8 clock pulses at the previous one.

#### **Read Multiple Registers**

#### Figure 6. Multiple bytes SPI read protocol (2 bytes example)

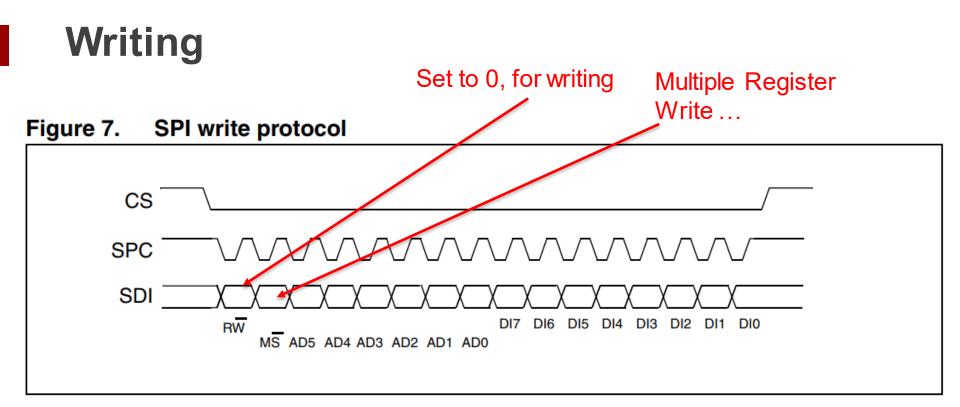

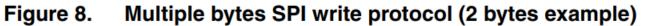

#### Write Multiple Registers

# **Raspberry Pi Python SPI**

```

#!/usr/bin/env python3

```

```

# A brief demonstration of the Raspberry Pi SPI interface, using the Sparkfun

# Pi Wedge breakout board and a SparkFun Serial 7 Segment display:

# https://www.sparkfun.com/products/11629

import time

import spidev

# We only have SPI bus 0 available to us on the Pi

bus = 0

# Device is the chip select pin. Set to 0 or 1, depending on the connections

device = 0

# Enable SPI

spi = spidev.SpiDev()

spi.open(bus, device)

# Set SPI speed and mode

spi.max speed hz = 500000

spi.mode = 0

readval = spi.xfer2([0x8F,0x00])

```

```

print(readval)

```

| Name                     | Tune | Register         | Address  | Default   | Function and<br>comment |  |  |  |  |

|--------------------------|------|------------------|----------|-----------|-------------------------|--|--|--|--|

| Name                     | Туре | Hex              | Binary   |           |                         |  |  |  |  |

| Reserved (Do not modify) |      | 00-07<br>0D - 0E |          |           | Reserved                |  |  |  |  |

| REF_P_XL                 | R/W  | 08               | 0001000  | 00000000  |                         |  |  |  |  |

| REF_P_L                  | R/W  | 09               | 0001001  | 0000000   |                         |  |  |  |  |

| REF_P_H                  | R/W  | 0A               | 0001010  | 00000000  |                         |  |  |  |  |

| WHO_AM_I                 | R    | 0F               | 0001111  | 10111011  | Dummy register          |  |  |  |  |

| RES_CONF                 | R/W  | 10               | 0010000  | 011111010 |                         |  |  |  |  |

| Reserved (Do not modify) |      | 11-1F            |          |           | Reserved                |  |  |  |  |

| CTRL_REG1                | R/W  | 20               | 010 0000 | 00000000  |                         |  |  |  |  |

| CTRL_REG2                | R/W  | 21               | 010 0001 | 00000000  |                         |  |  |  |  |

| CTRL_REG3                | R/W  | 22               | 010 0010 | 00000000  |                         |  |  |  |  |

| INT_CFG_REG              | R/W  | 23               | 0100011  | 0000000   |                         |  |  |  |  |

#### Table 14. Registers address map

INDIANA UNIVERSITY BLOOMINGTON